Quantum computing Ph.D. student

University of Chicago jchadwick@uchicago.edu

CV Github Google Scholar arXiv LinkedIn ORCiD

About

I am a final-year computer science Ph.D. student at the University of Chicago studying quantum computer systems with Fred Chong. Previously, I graduated from Carnegie Mellon University in 2022 with a B.S. in physics and a minor in computer science.

I’m interested in computer systems/architecture research for quantum computing. I believe that co-designing quantum hardware and software is essential to make scalable quantum computing a reality. I am currently working on tailoring QEC to hardware and improving real-time decoding. Previously, I have published work on software mitigation of time-varying noise (such as cosmic ray impacts and shifting two-level system defects) in the surface code, quantum control pulse optimization, and a pair of papers on compiling with ququarts.

In the summer of 2024, I interned with the quantum computing team at Intel, where I explored the relationship between qubit configuration and two-qubit gate schedules, providing guidance for Intel’s quantum roadmap. Check out the publication!

In the summer of 2025, I once again interned at Intel, where I studied experimental crosstalk data and developed internal simulation tools in Python and C++ to model the impact of capacitive crosstalk in realistic QEC schedules.

Selected Research

(under review)

Jason D. Chadwick, Joshua Viszlai, Willers Yang, and Frederic T. Chong [project] [.pdf] [arXiv] We propose SNAQ, a near-term-manufacturable surface code architecture for spin qubits that significantly reduces chip area per logical qubit and improves logical clock speed.

Erasure Minesweeper: exploring hybrid-erasure surface code architectures for efficient quantum error correction

QCE 2025

Jason D. Chadwick*, Mariesa H. Teo*, Joshua Viszlai*, Willers Yang*, and Frederic T. Chong [project] [.pdf] [arXiv] [talk] [slides] We explore a hybrid-erasure architecture for surface code error correction, studying strategies for placement of erasure qubits and tradeoffs between per-qubit cost and logical performance. * indicates equal contribution

Physical Review A 111, 052616 (2025)

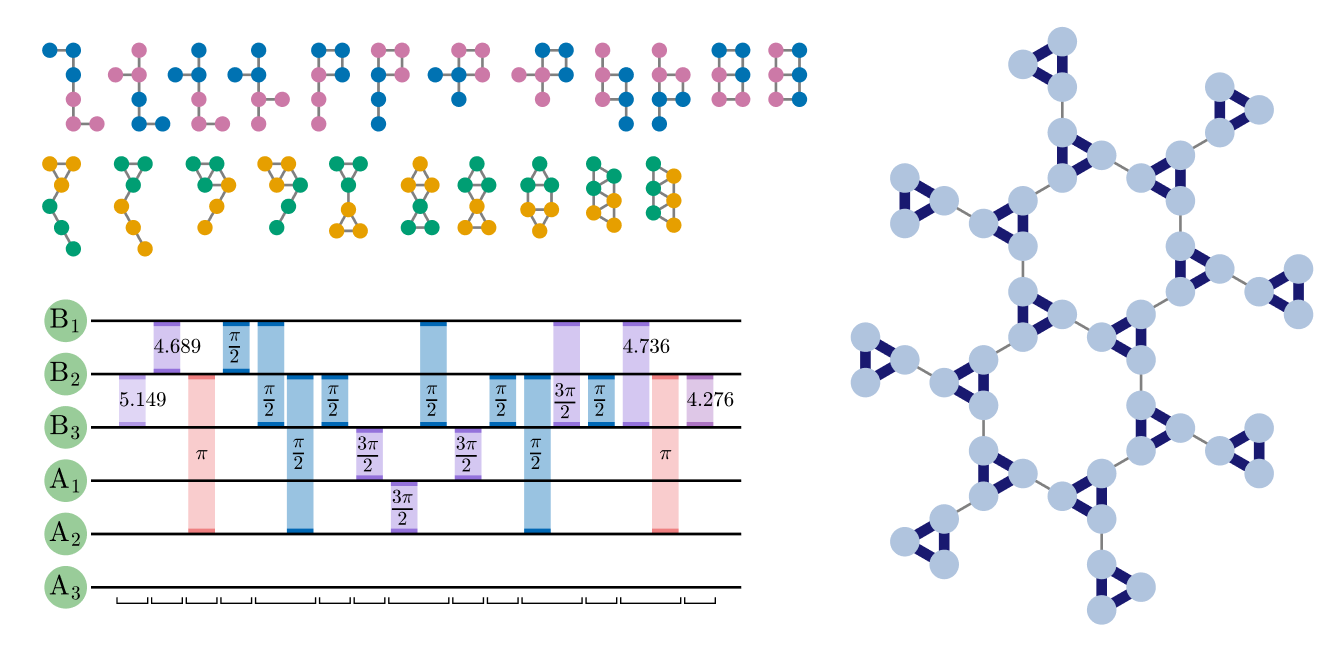

Jason D. Chadwick, Gian Giacomo Guerreschi, Florian Luthi, Mateusz T. Mądzik, Fahd A. Mohiyaddin, Prithviraj Prabhu, Albert T. Schmitz, Andrew Litteken, Shavindra Premaratne, Nathaniel C. Bishop, Anne Y. Matsuura, and James S. Clarke [project] [.pdf] [publication] [arXiv] [talk] [data] We develop an optimization method to map exchange-only (EO) qubit pulse sequences to arbitrary connectivities. We explore the impact of EO qubit topology on quantum error correction performance.

ISCA 2025

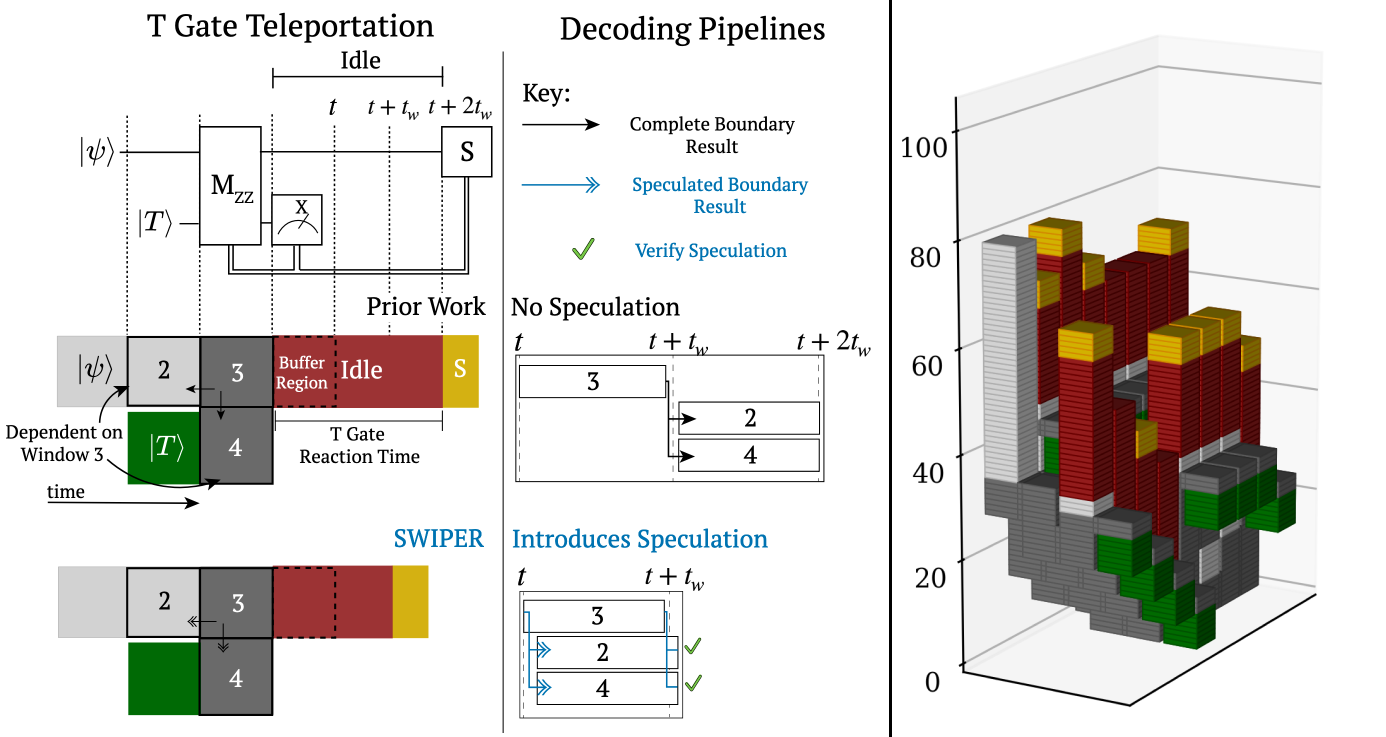

Joshua Viszlai*, Jason D. Chadwick*, Sarang Joshi, Gokul Ravi, Yanjing Li, and Frederic T. Chong [project] [.pdf] [publication] [arXiv] [code] We translate branch prediction from classical architecture to the problem of windowed decoding of quantum-error-corrected algorithms. We show that this can consistently reduce application benchmark runtimes by 40%. * indicates equal contribution

Averting multi-qubit burst errors in surface code magic state factories

QCE 2024

Jason D. Chadwick, Christopher Kang, Joshua Viszlai, Sophia Fuhui Lin, and Frederic T. Chong [project] [.pdf] [publication] [arXiv] [talk] [slides] [code] We design an efficient method to avoid cosmic ray errors in magic state factories, significantly reducing the qubitcycle cost of mitigating these errors.

(in preparation)

Jason D. Chadwick*, Christopher Kang*, Sophia Fuhui Lin, and Frederic T. Chong [project] [slides] We show that surface code magic state factories are vulnerable to varying hardware performance and can magnify hardware degradation. To alleviate this problem, we introduce Verity, a resilient kernel for magic state distillation. * indicates equal contribution

Efficient control pulses for continuous quantum gate families through coordinated re-optimization

QCE 2023

Jason D. Chadwick and Frederic T. Chong [project] [.pdf] [publication] [arXiv] [talk] [poster] [code] We present a method that allows quantum hardware to execute arbitrary operations at the pulse level by interpolating between a small number of known reference pulses. We demonstrate the procedure on the continuous space of all two-qubit operations.

ISCA 2023

Andrew Litteken, Lennart Maximilian Seifert, Jason D. Chadwick, Natalia Nottingham, Tanay Roy, Ziqian Li, David Schuster, Jonathan M. Baker, and Frederic T. Chong [project] [.pdf] [publication] [arXiv] We extend our previous work on qubit-to-ququart compression to specifically optimize three-qubit gates such as the Toffoli gate. We also find significant advantages in using Z-type multi-bit operations instead of X-type operations.

ASPLOS 2023

Andrew Litteken, Lennart Maximilian Seifert, Jason D. Chadwick, Natalia Nottingham, Jonathan M. Baker, and Frederic T. Chong [project] [.pdf] [publication] [arXiv] We consider selectively compressing pairs of qubits into single four-state ququarts. We generate efficient "partial" operations between ququarts and qubits, which motivates a compiler that can transform any quantum circuit into this framework.

QCE 2022

Lennart Maximilian Seifert*, Jason D. Chadwick*, Andrew Litteken, Frederic T. Chong, and Jonathan M. Baker [project] [.pdf] [publication] [arXiv] [poster] We present a method to iteratively obtain short-duration quantum control pulses when it is not possible to directly modify the objective function. We use this to find gate durations for high-radix logic gates that scale better than expected. * indicates equal contribution

Nuclear Fusion 61 046024

Mark D. Boyer and Jason D. Chadwick [project] [.pdf] [publication] [poster] [slides] We develop a neural network to accurately predict cross-sectional shapes of plasma density and pressure on the NSTX-U fusion reactor. The network runs orders of magnitude faster than existing physics-based code.

Projects

[code] Collection of useful utility functions that I have accumulated while working on various quantum computing projects. Includes flexible state/process tomography experiments, Hamiltonian builders, many quantum logic gates, and more miscellaneous reuseable code.

[project] [live web game] [code] A 2D platformer game where the player can slow and reverse the flow of time to solve increasingly complex puzzles. Inspired by the game Portal and the movie Tenet. A live web version is hosted on this site. Made with Unity and C#.

[project] In the summer of 2019, I worked with Ken Olum at the Tufts Institute of Cosmology to study the properties of smooth cosmic string loops. I began the summer running computational simulations of cosmic strings and later transitioned to working on a mathematical proof that smooth cosmic string loops will always decay.